# 长龙国际股份有限公司

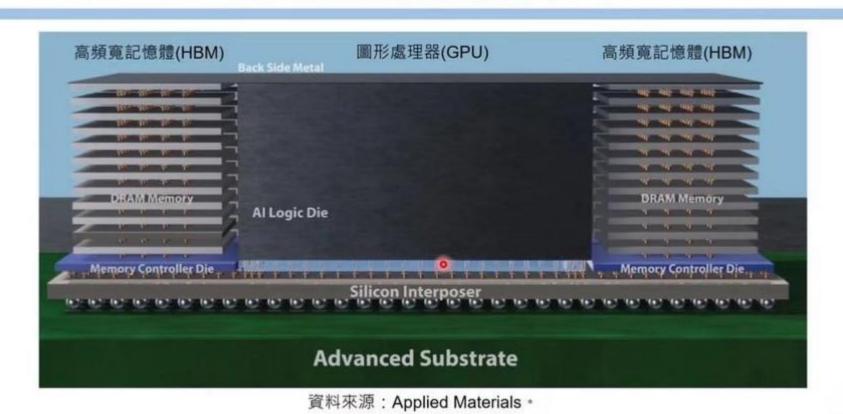

与新马地区、上海地区合作 启动先进的HBM半导体 COWOS的3D封装项目

https://clisemi.com/

## 公司简介

长龙国际设立于 2017 年 1 月,我们的团队专注于先进 封装厂的整厂输出及绿能技术开发,从技术开发到生产 实施。拥有的技术发明基础上,汇聚了一群半导体及绿 能领域的专家,确保项目技术先进性和生产高效。

## 公司沿革

2017年

公司成立

2017 年至2020 年 HBM/3D封装及专利布局。

和韓國Pro Test销售额 5000 万美元/每年约150人。

及 ITEST(艾特半导体) 销售额1.2亿美元/每年约 850人。

2021年

研发增程摩托车。

2022年

研发电动脚踏车。

2023年至2024年 研发无人机增程动力系统。

2025年

研发机器人动力增程背包专利。

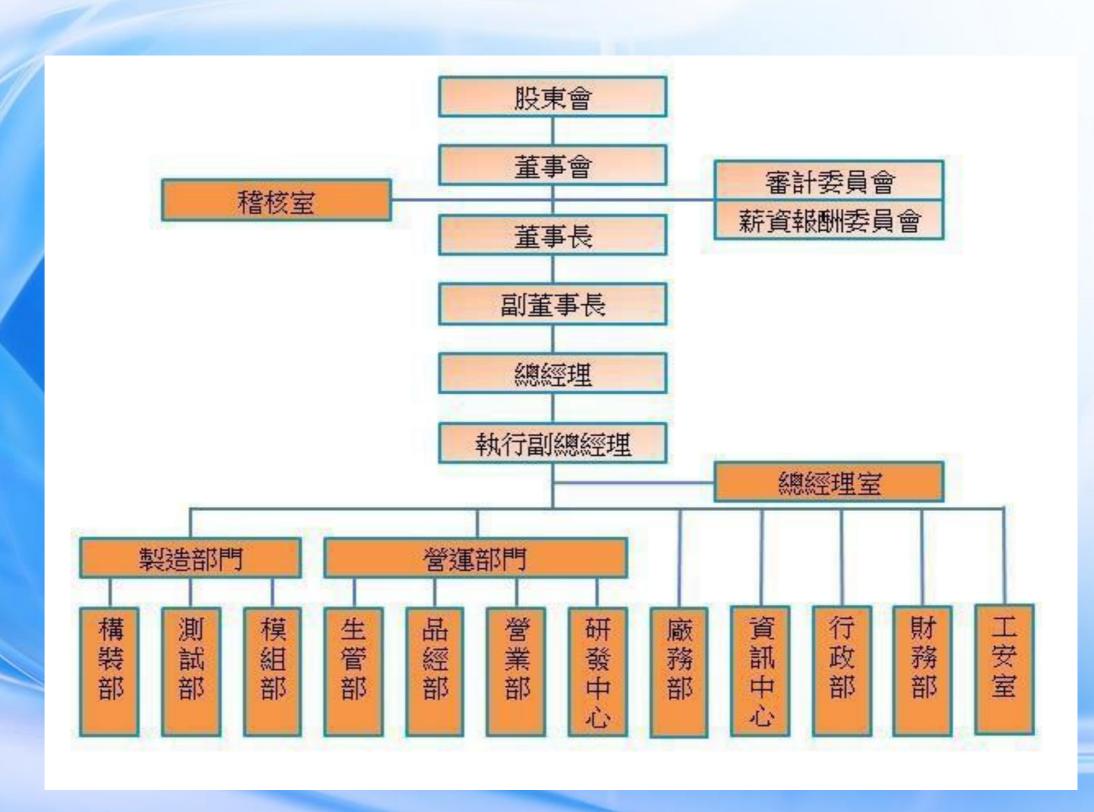

## 公司组织结构

## 团队成员

| 团队       | 成员     | 学经历 | 其它         |

|----------|--------|-----|------------|

| 运营团队     | 5~7人   |     | 经由董事会聘任    |

| 生产技术专家团队 | 50~70人 |     | 台湾/韩国现职工程师 |

| 品质管理专家团队 | 15~25人 |     | 台湾/韩国现职工程师 |

| 市场分析专家   | 7~9人   |     | 台湾现职工程师    |

## 台湾技术团队成员及其经历介绍

| 职称    | 姓名  | 个人经历                     |

|-------|-----|--------------------------|

| 技术总监  | 沈明东 | 超过30年半导体组件封装、电子电路设计、电池材料 |

|       |     | 研发经验                     |

| 资深顾问  | 杨博士 | 清华大学材料科技博士学位             |

|       |     | 剑桥大学锂电池博士学位              |

| 营运执行长 | 林福男 | 大同工学院学士                  |

|       |     | 大同股份有限公司                 |

|       |     | 开发、设计、生产、管理经验 35 年以上     |

| 资深工程师 | 王先生 | 首席技术总监                   |

|       |     | 开发设计经验 15 年以上            |

|       |     | 半导体封测研发经验 10 年以上         |

### 韩国 技术团队:由多名研发工程师组成,具有丰富的

### HBM技术研发和应用经验

#### HBM Project(Packaging& Test)

#### 1) Basic personal composition(Packaging)

| NAME            | CAREER         | WORK EXPERENCE                 | REMARK             |

|-----------------|----------------|--------------------------------|--------------------|

| JJKIM           | about 30 Years | SK Hynix& AT semicon           | Gensral Affairs    |

| LEE             | about 15 Years | SK Hynix Substrate Process     | eng'rs             |

| Park            | about 5 Years  | SK Hynix Substrate Process     | eng'rs             |

| KIM             | about 10 Years | SK Hynix Bumping               | Preocess eng'rs    |

| СНА             | about 6 Years  | SK Hynix/Domestic Fabless Bump | ing Process eng'rs |

| LEE             | about 10 Years | SK Hynix Interpose Process     | eng'rs             |

| KIM             | about 10 Years | SK Hynix & OSAT HBM Process    | eng'rs             |

| КІМ             | about 10 Years | SK Hynix & OSAT HBM Process    | eng'rs             |

| Others(4people) | about 5 Years  | Domestic OSAT Assistant        |                    |

Page 1/2

#### HBM Project(Packaging& Test)

#### 2) Basic personal composition(Test)

| NAME             | CAREER         | WORK EXPERENCE                      | REMARK                      |

|------------------|----------------|-------------------------------------|-----------------------------|

| JJKIM            | about 30 Years | SK Hynix& AT semicon                | Gensral Affairs (Duplicated |

| LEE              | about 15 Years | SK Hynix Dram Test                  | eng'rs                      |

| LEE              | about 10 Years | SK Hynix                            | Nand Test eng'rs            |

| JOUNG            | about 10 Years | OSAT or Domestic Fabless Logic Test | eng'rs                      |

| КІМ              | about 5 Years  | Domestic Fabless or Design Comany   | Logic Test eng'rs           |

| Others(3 people) | about 5 Years  | Domestic OSAT Assistant             |                             |

#### 3) Detail plan

- Establish detailed strategies for each step(Prepare a Test base in conjunction with 3D Packaging development)

- The Test Engineer composition is centered on local personnel, and additional personnel are prepared for early SET UP, Yiled up, etc.

- Separate establishment of overall personal paln,etc.(Engineering/Maintenance/Production.etc)

核心团队:包括多名在半导体行业有多年经验的技术专家和市场营销专家,其中CTO在内存技术研发领域有超过20年的经验。

### Pro Test和ITEST(AT semicon)前董事長履歷

#### **Personal Career**

個人情報

姓名:金 鎖宙(KIM JIN JOO),63歲

#### 學歷

- 漢陽大學校 電氣工學科(工學士)

- 優陽大學校 大學院 電氣工學科(工學碩士)

#### 主要 經力

1986~2002: LG半導體 Test技術 室長 2003~2019: AT semicon 代表理事 2019~2021: HYTC Advisor

2021~現在: KH TECH 代表理事

#### Detail Career

#### 1986~2002 LG华導體

- Memory Test Program開發& Development Engineer

- Memory(Dram/Nand)/MCU/C MOS image semsor/ASIC Test Eng'rs Team Leader

- 72M Rambus DRAM 國內最初 Test Program開發

#### 2003~現在 Pro Test/I TEST/AT semicon/KH TECH

2002. Pro Test設立/Test House事樂開始

2006. I TEST合件

- Dram&Flash Memory(SK Hynix),System LSI(Samsung),Fabless會社 Test實施

2007. Multi Chip Test & AP Chip Test 開始

2011. 韓國 KOSDAQ上場

2012. Mobile用 DRAM Test實施

2014. Semitech引受合併

- Package and Test House 事業擴大

2019~現在 半導體 Consultanting

## 韩国技术团队成员及其经历介绍

|   | 职称    | 姓名               | 个人经历               |

|---|-------|------------------|--------------------|

|   | 经理兼董事 | GM KIM(Director) | 研发部 (另带领约 10 干部成员) |

|   | 经理    | HJ KIM           | 生技部 (另带领约 50 成员)   |

| 7 | 经理    | CJ Sung          | 量测部 (另带领约 15 成员)   |

|   | 经理    | BHKIM            | 质量管理部 (另带领约 15 成员) |

|   | 经理    | GH Shin          | 设备部 (另带领约 12 成员)   |

## 商业计划

### 1. 全面的日程

### 1)日程安排经过部门

| item                              | Detail schedule |      |

|-----------------------------------|-----------------|------|

| Establish a specific plan         | ~2 Week         |      |

| Equipment ordering/receiving      | → About3~4Month |      |

| Secure Key Man                    | About 2Month    |      |

| Human Resources and Training      | About 3Month    |      |

| Overall production management     | About 2Month    |      |

| 1Line set up                      | About 2 Week    | cs   |

| Customer Qual                     | About 2~3 We    | eeks |

| General preparation(computer.etc) | About 2~3 We    | eeks |

| Others                            |                 |      |

2) 考虑 这 总体日程安排如下 作为 这 工厂 完成 时间表和 设备 介绍,这是 可能的 到 缩短 这 日程。

- 它 有可能 到 缩短 这 日程 时期 当 详细的 计划 已建立 和 这 设备订购 单 已推广。

### 2. 投资 数量 和 必需的 区域

1)投资数量(1线路设置&附加计划)和需要区域

| Div               | ision                 | 1 Line set up                  | Additional equipment           | Total amount                    |

|-------------------|-----------------------|--------------------------------|--------------------------------|---------------------------------|

| lymactmant        | Packaging             | USD 7.7M\$                     | USD 34.6M\$                    | USD 42.3M\$                     |

| lvnestment amount | TEST                  | USD 6.4M\$                     | USD 7.7M\$                     | USD 14.0\$                      |

| amount            | sum                   | USD 14.0M\$                    | USD 42.3M\$                    | <u>USD 56.3M\$</u>              |

| Area required     | PKG                   | Clean room 3,300m <sup>2</sup> | Clean room 8,250m <sup>2</sup> | Clean room 11,550m <sup>2</sup> |

|                   | TEST                  | Clean room 1,650m <sup>2</sup> | Clean room 1,650m <sup>2</sup> | Clean room 3,300m <sup>2</sup>  |

|                   | etc(Office)           | 660m²                          |                                | 660m²                           |

|                   | etc(education)        | 990m²                          |                                | 990m²                           |

|                   | <b>Total required</b> |                                |                                | Total 16,500m <sup>2</sup>      |

Note \*) Class division is 50% prepared for class 1000 and 10,000

2) 这全部的投资是美元 5630万美元和 这所需面积为16,500 m<sup>2</sup>

### 3. 销售量和操作利润

1) 销售量和操作利润(基于在年)

| Div    | ision /    | 1 Line set up | Additional equipment | <b>Total amount</b> |

|--------|------------|---------------|----------------------|---------------------|

|        | Packaging  | USD 16.9M\$   | USD 83.1M\$          | USD 100.0M\$        |

| Sales  | TEST       | USD 2.3M\$    | USD 2.6M\$           | USD 5.0\$           |

|        | sum        | USD 19.2M\$   | USD 89.2M\$          | <u>USD 105.0M\$</u> |

| Operat | ing profit | 8.30%         | 24.30%               | 21.30%              |

Note \*1) Sales will be made after normal set up is completed.

- \*2) Equipment deprecication is calculated on a 5-year straight-line basis.

- \*3) The material cost of packaging is assumed to be 60%.

2) 和额外的投资,这速度返回预计到是大约20%到期的到规模经济。

## 技术优势分析

长龙的3D PoP和3D WLP技术具有显着的替代潜力:

• 3D PoP凭借其多层堆叠和高密度互连结构,适合作为SolC的替代方案, 尤其在高性能计算和 5G基站等高带宽需求的应用中。

• 3D WLP则以较高的良率和较简化的散热设计,能够替代WoW,特别适合对芯片面积利用率和密度要求较高的场景。

表:台积电先进封装工艺与公司技术对比

| 衣,口似 <b>出</b> 儿处封衣工乙一刀以小刈山 |                  |                                                   |                    |            |  |

|----------------------------|------------------|---------------------------------------------------|--------------------|------------|--|

| 封装技术                       | 技术全称             | 特点与优势                                             | 适用场景               | 可对比技术      |  |

| CoWoS                      | Chip-on-Wafer-   | 提供高带宽互连和                                          | 高性能计算、AI应          |            |  |

|                            | on-Substrate     | 高效热管理·适合<br>高性能计算;常用<br>于2.5D封装                   | 用(如GPU、高性<br>能处理器) |            |  |

| InFO                       | Integrated Fan-  | 无基板扇出型封                                           | 移动处理器、IoT设         |            |  |

|                            | Out              | 装,适合移动和IoT<br>设备,封装薄、信<br>号传输性能优越,<br>提升晶圆利用率     | 备                  |            |  |

| SoIC                       | System on        | 3D堆叠封装技术,                                         | 高性能计算、5G基          | 长龙 3D PoP  |  |

|                            | Integrated Chips | 支持多芯片垂直堆<br>叠,带来更高系统<br>集成度和更低功<br>耗,减少延迟         | 站                  | (有FAB条件限制) |  |

| WoW                        | Wafer-on-Wafer   | 晶圆直接堆叠技<br>术,提高芯片面<br>积利用率,增强<br>密度集成,适合<br>高密度需求 | 高密度集成应用            | 长龙 3D WLP  |  |

| TSMC-3DFabric™             | TSMC-SoIC and    | 集成多个封装技术                                          | 人工智能、5G、云          |            |  |

| Platform                   | TSMC-3DFabric™   | •                                                 | 计算、高性能计算           |            |  |

|                            | Platform         | 和InFO),提供                                         | 应用                 |            |  |

|                            |                  | 2D、2.5D和3D封<br>装的定制化选择,<br>提高整体系统性能               |                    |            |  |

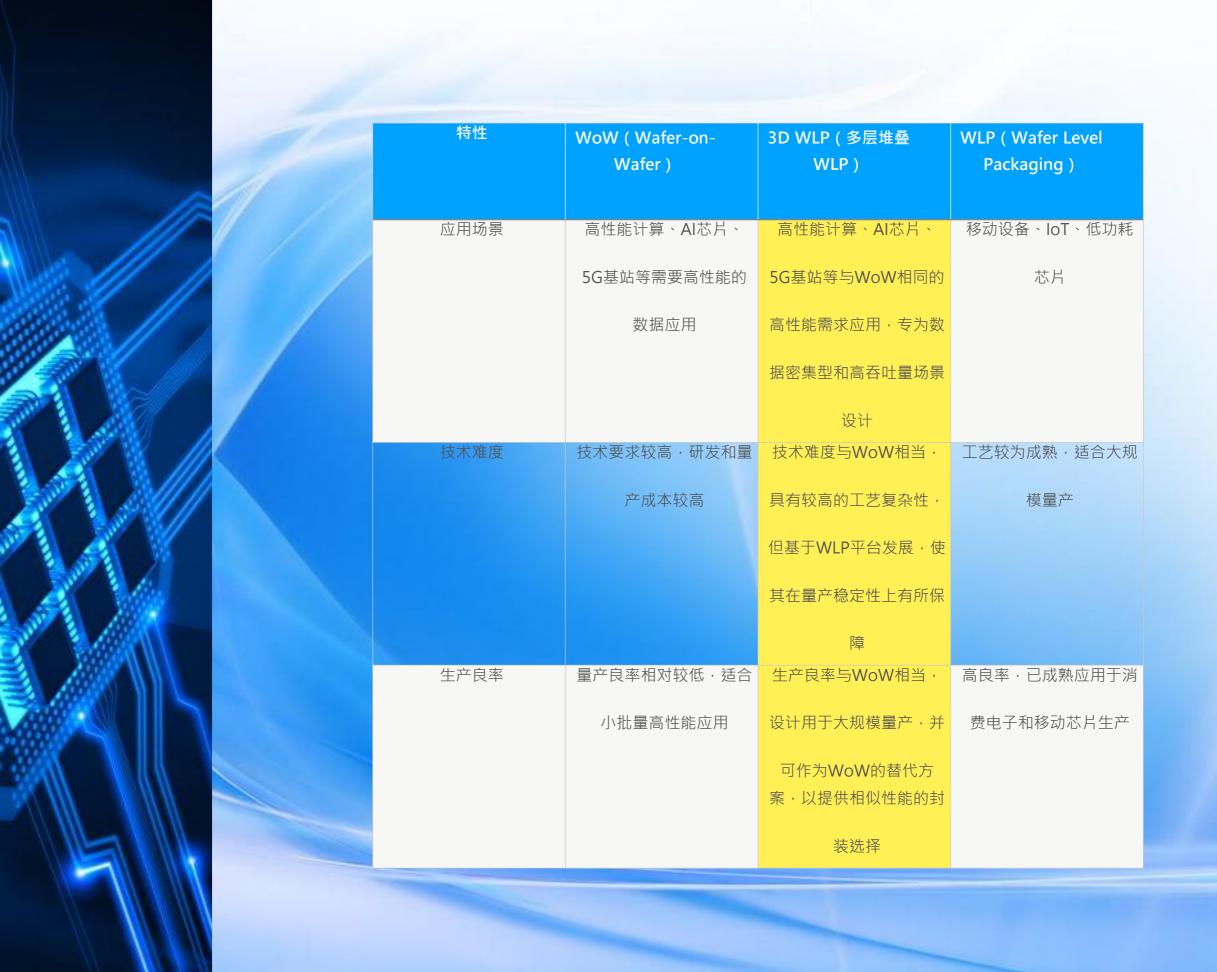

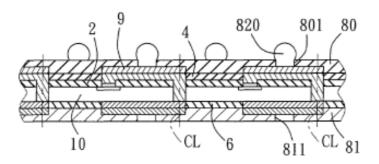

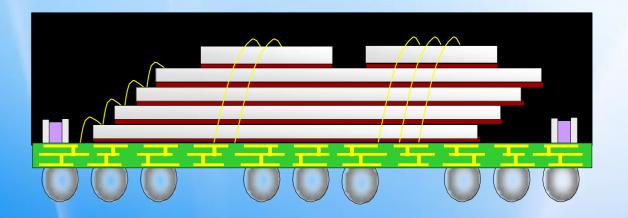

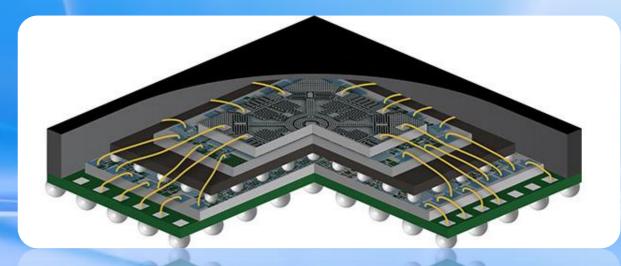

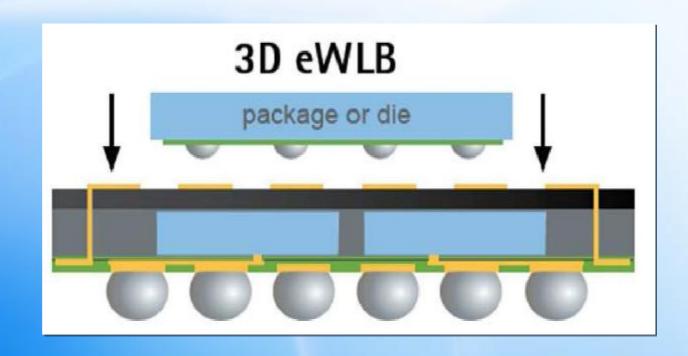

## 3D WLP 多层堆叠封装

3D WLP 多层堆叠封装在结构上融合了 WLP 和 WoW 的优势,具有较高的带宽密度和较短的互连 路径,同时在性能与功耗之间取得平衡。其散热需求与 WoW 相当,适用于高性能计算、AI 芯片和 5G 基站等场景,并提供了比单层 WLP 更高的集成度。3D WLP 的工艺复杂性和技术难度与 WoW 相当,生产良率也接近 WoW,使其在高性能需求应用中成为 WoW 的替代方案,有助于满足数据 密集型和大规模量产需求。

表:长龙 3D WLP 与 WLP 和 WoW 封装技术特性对比

| 特性   | WoW ( Wafer-on- | 3D WLP (多层堆叠 | WLP ( Wafer Level |

|------|-----------------|--------------|-------------------|

|      | Wafer )         | WLP)         | Packaging )       |

| 封装方式 | 晶圆堆叠封装,将两个或     | 多层堆叠封装,通过在   | 晶圆级封装・在晶圆制造       |

|      | 多个完整的晶圆直接垂直     | WLP基础上进行多层垂直 | 阶段直接封装芯片          |

|      | 堆叠              | 堆叠,兼具WLP的封装薄 |                   |

|      |                 | 型化特点与WoW的3D堆 |                   |

|      |                 | 叠特性          |                   |

| 封装结构 | 3D堆叠封装;通过垂直     | 3D堆叠封装,多层结构  | 2D封装;单层封装在单       |

|      | 堆叠晶圆实现高密度集成     | 使芯片面积利用率提高;  | 一平面上              |

|      |                 | 可通过垂直互连方式实现  |                   |

|      |                 | 多层电路的高效连接    |                   |

| 集成度  | 高集成度;支持复杂系统     | 中高集成度;相比传统   | 集成度较低;适合较小封       |

|      | 级封装和高密度集成       | WLP更高密度,但通常不 | 装尺寸需求             |

|      |                 | 及完全的3D堆叠封装如  |                   |

|      |                 | WoW的集成度      |                   |

| 性能特点 | 提供高带宽低延迟互连,     | 通过垂直堆叠带来较高的  | 较低的互连密度和带宽,       |

|      | 适合高性能和大数据吞吐     | 带宽密度和更短的互连路  | 适用于低功耗和中等性能       |

|      | 需求              | 径;在性能和功耗之间提  | 需求                |

|      |                 | 供平衡,适合性能和功耗  |                   |

|      |                 | 要求适中的应用      |                   |

| 散热能力 | 较高散热需求,适合高性     | 相较于单层WLP具有更高 | 散热能力较低,由于封装       |

|      | 能应用,通常需要更复杂     | 的散热需求,但由于封装  | 较薄适合低至中功耗设备       |

|      | 的散热设计           | 较薄通常比WoW的散热  |                   |

|      |                 | 设计更为简化,可通过外  |                   |

|      |                 | 部散热方案进行优化    |                   |

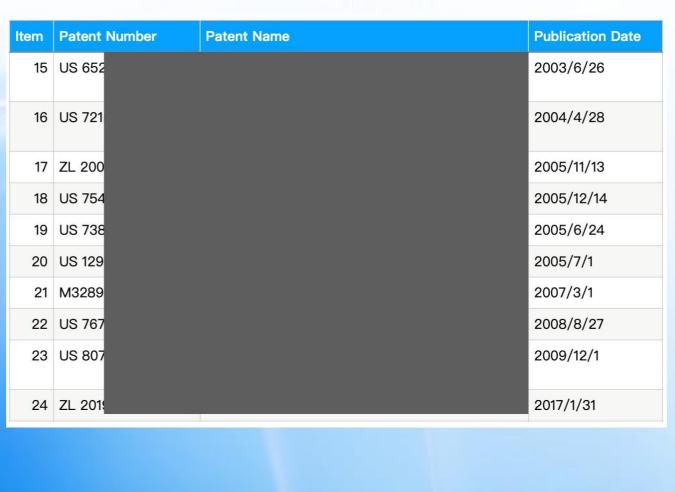

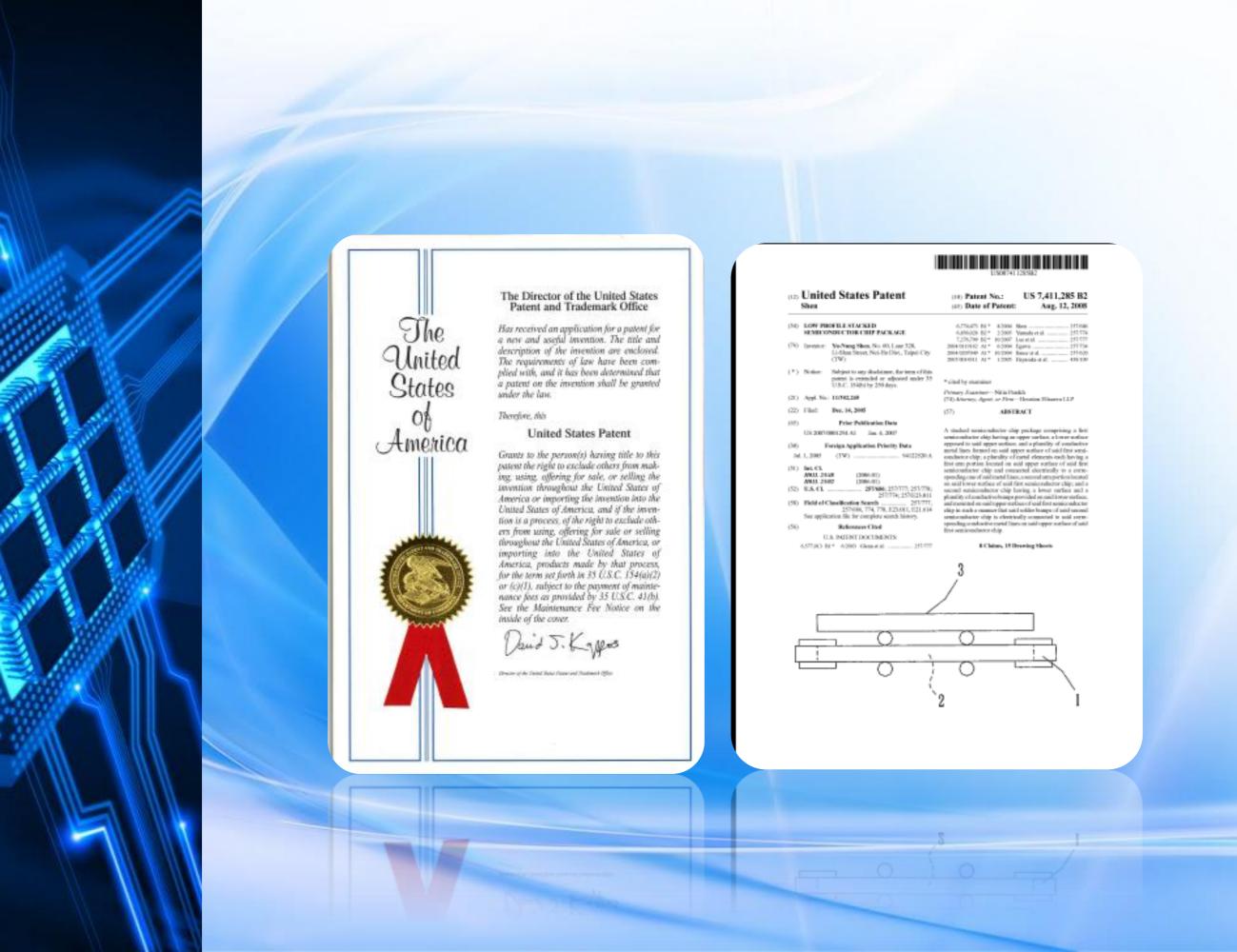

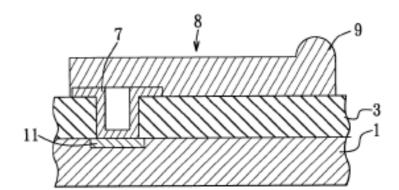

### 专利布局

长龙的专利布局涵盖了半导体封装、低轮廓结构、散热装置及多层互连结构等核心领域,体现了其 在 高密度集成、散热管理和低轮廓封装等关键技术上的优势。例如,涵盖了多层集成和电气连接优 化方 法,为高性能需求提供了稳健的基础;而散热相关专利则确保了高集成度芯片的热管理效率。 整体布局支持长龙在先进封装领域的竞争力,并有助于进一步优化其产品性能和市场覆盖。

表:与先进封装有关专利(标记为主专利)

| Item | Patent Number | Patent Name                                                                                                | Publication Date |

|------|---------------|------------------------------------------------------------------------------------------------------------|------------------|

| 1    | US 677        | onductor chip module                                                                                       | 1999/9/28        |

| 2    | US 642        | d for mounting a semiconductor chip on a ate and semiconductor device adapted for ing on a substrate       | 2000/10/16       |

| 3    | US 670        |                                                                                                            | 2000/7/18        |

| 4    | US 662        |                                                                                                            | 2000/8/4         |

| 5    | US 643        | onductor device adapted for mounting on a ate                                                              | 2001/1/18        |

| 6    | US 657        |                                                                                                            | 2001/11/13       |

| 7    | US 658        |                                                                                                            | 2001/11/13       |

| 8    | US 673        |                                                                                                            | 2001/3/16        |

| 9    | US 660        | d for mounting a semiconductor chip on a<br>ate and semiconductor device adapted for<br>ing on a substrate | 2002/4/11        |

| 10   | US 661        | d for mounting a semiconductor chip on a ate and semiconductor device adapted for ing on a substrate       | 2002/4/17        |

| 11   | US 667        |                                                                                                            | 2003/1/8         |

| 12   | US 7710       |                                                                                                            | 2003/11/19       |

| 13   | US 768        |                                                                                                            | 2003/11/19       |

| 14   | US 124        |                                                                                                            | 2003/5/12        |

长龙在2002年形成了针对 substrate 的关键专利布局,锁定了多个涉及芯片在基板上的安装方法与 封装结构的专利,这些早期的创新限制了其他大厂的技术路线。专利相继发布,进一步巩固了长龙 在基板相关技术的市场优势。这些专利的布局确保了在多芯片模块的封装和安装方法上,长龙在行业中保持先发地位,对其他大厂在相关领域的技术开发造成了显着限制。

### 主要专利对3D WLP和3D PoP的发展优势

作为3D WLP和3D PoP发展的关键技术布局,长龙的专利组合增强了其在多层封装中的优势:

- 提升了电气连接和安装精度,优化了多层封装的连接可靠性;

- 微细互连技术则在多芯片模块中提升了结构灵活性和稳定性;

- 通过简化工艺和优化电气连接,提高了3D精密封装的效率;

- 多层互连结构则专注于高密度需求,尤其适合3D WLP的应用。这些布局奠定了长龙在3D封装领域的稳固地位。

### 表:长龙主要专利内容描述及产业效果

| 表:长 <i>ル</i> 主要专利内谷抽処及产业效果 |                                    |                                                                                             |                                                |  |

|----------------------------|------------------------------------|---------------------------------------------------------------------------------------------|------------------------------------------------|--|

| Item                       | 专利名称                               | 概要描述                                                                                        | 产业效果                                           |  |

| 2                          | Method f<br>semiconc<br>a substra  | 描述了在芯片焊盘表面形成绝缘层和导电体,通过隔离层中的接触腔和通孔连接芯片和基板焊点。此技术优化了芯片电气连接,提升了安装精度和可靠性,适合复杂电路封装。               | 为复杂电路封装提供早期电气<br>连接解决方案,推动高精度、<br>高可靠性封装的普及。   |  |

| 5                          | Semicono<br>adapted t<br>on a subs | 提供一种通过微细互连技术将芯片焊盘与基板焊点连接的装置,增强了电气连接和结构可靠性,特别适用于多芯片模块封装,提高了封装的稳定性,并在早期阶段限制了竞争对手技术路线。         | 提升多芯片模块封装的稳定性,成为产业标准,降低竞争者在电气互连方面的技术发展空间。      |  |

| 9                          | Method f<br>semicond<br>a substra  | 介绍了在芯片焊盘上形成导电凸块并涂<br>覆光刻胶层的技术,通过在光刻胶层中<br>形成通孔并填充金属材料实现稳定连<br>接,提升了装配精度和电气性能,简化<br>了传统封装流程。 | 优化装配精度并简化流程,为<br>高密度和小尺寸芯片封装提供<br>高效生产路径。      |  |

| 10                         | Method fi<br>semicond<br>a substra | 使用多层导电结构提升芯片与基板的电气连接,在焊盘表面涂覆光刻胶层形成导电凸块,并通过通孔和多层互连结构增强电气连接,适用于高密度多芯片封装,优化了装配过程和性能。           | 支持高密度封装发展,促进多<br>层互连技术的成熟和产业推<br>广,适用于高性能芯片模块。 |  |

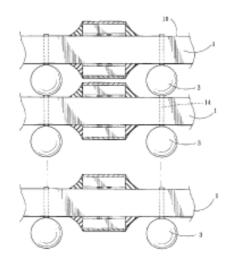

## 3D封装专利清单

| /_ |    |                  |                                                                                                                      |  |  |  |

|----|----|------------------|----------------------------------------------------------------------------------------------------------------------|--|--|--|

|    | 項目 | 專利號              | 案弓名稱                                                                                                                 |  |  |  |

|    | 1  | US7383630        | Method for making a circuit plate                                                                                    |  |  |  |

|    | 2  | US6774473        | Semiconductor chip module                                                                                            |  |  |  |

|    | 3  | US6420788        | Method for mounting a semiconductor chip on a substrate and semiconductor device adapted for mounting on a substrate |  |  |  |

|    | 4  | US6437448        | Semiconductor device adapted for mounting on a substrate                                                             |  |  |  |

|    | 5  | US7176573        | Semiconductor device with a multi-level interconnect structure and method for making the same                        |  |  |  |

|    | 6  | I241009          | 一種形成玄砲凸塊的方法及具布如此形成之電凸塊的裝置                                                                                            |  |  |  |

|    | 7  | I292178          | 堆疊式半導體晶片封裝體                                                                                                          |  |  |  |

|    | 8  | US7411285        | Low profile stacked semiconductor chip package                                                                       |  |  |  |

|    | 9  | ZL200510117763.5 | 堆疊式半導體晶片封裝體                                                                                                          |  |  |  |

|    | 10 | US8076775        | Semiconductor package and method for making the same                                                                 |  |  |  |

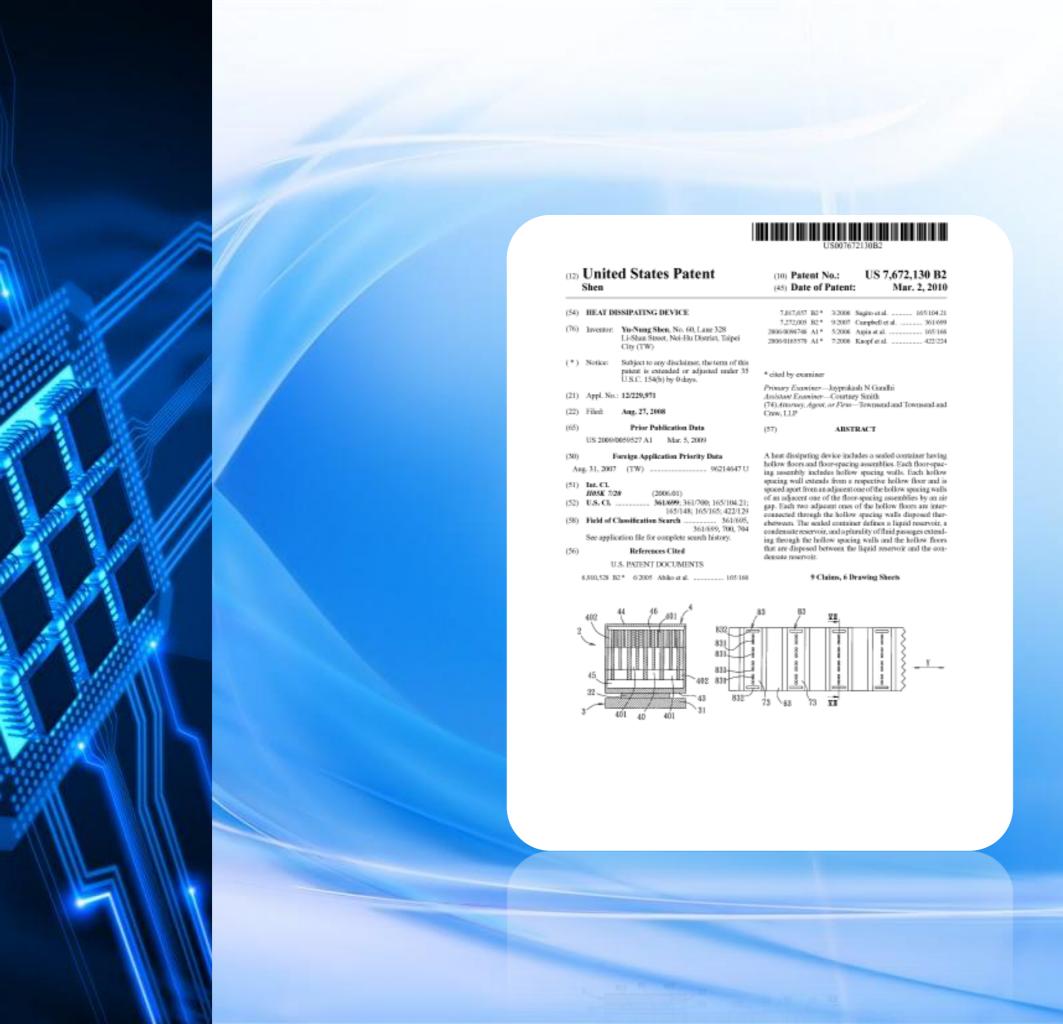

|    | 11 | US7672130        | Heat dissipating device                                                                                              |  |  |  |

|    | 12 | ZL201110036515.3 | 散熱裝置                                                                                                                 |  |  |  |

## 长龙国际与新马地区、大陆合肥地区 合作3D封装相关项目

(12) United States Patent Shen

(10) Patent No.: US 8,076,775 B2 (45) Date of Patent: Dec. 13, 2011

(54) SEMICONDUCTOR PACKAGE AND METHOD FOR MAKING THE SAME

(76) Inventor: Yu-Nung Shen, Taipei (TW)

(\*) Notice: Subject to any disclaimer, the term of this potent is extended or adjusted under 35 U.S.C. 154(b) by 73 days.

(21) Appl. No.: 12/357,334 (22) Filed: Jan. 21, 2009

(65) Prior Publication Data

US 2009/0194863 A1 Aug. 6, 2009

Foreign Application Priority Data (30)

Feb. 1, 2008 (TW) ...... 97104403 A

(51) Int. Cl. H0H. 23/94 (2006.01) (52) U.S. Cl. . 257/730; 257/826; 257/774; 257/E23.023; 257/E23.069; 257/E23.125; 438/106; 438/127; 361/777

See application file for complete search history.

(56)References Cited

> U.S. PATENT DOCUMENTS

\* cited by examiner

Primary Evantuer — William D Coleman

Assistant Económer — Su Kim (74) Attorney, Agent, or Firm — Christie, Parker & Hale,

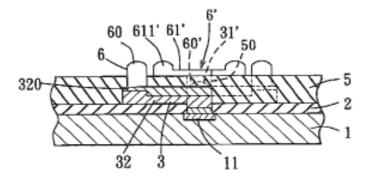

#### (57)ABSTRACT

A semiconductor pockage includes: a semiconductor sub-strate; an inner insulator keyer formed on the substrate; at least one internal wiring extending from a front side of the sub-strate along one of lateral sides of the substrate to a rear side of the substrate; a first outer insulator layer disposed at the front side of the substrate, formed on the internal wiring, and formed with at least one wire-connecting hole; and a second outer insulator layer disposed at the near side of the substrate, formed on the internal wiring, and formed with at least one wire-connecting hole which exposes a portion of the internal

7 Claims, 8 Drawing Sheets

#### (12) United States Patent

Shen

(10) Patent No.: US 6,774,473 B1

(45) Date of Patent: Aug. 10, 2004

| (54) | SEMILO   | NIPOCTOR CHIP  | MODULE         |  |

|------|----------|----------------|----------------|--|

| (75) | Inventor | Mine-Tune Shop | dE No. 52 Sec. |  |

Ming-Tung Shen, 4F, No. 52, Sec. 2, Chung-Shan N. Rd., Taipei (TW)

(73) Assignee: Ming-Tung Shen, Taipei (TW)

(\*) Notice: Subject to any disclaimer, the term of this patent is extended or adjusted under 35 U.S.C. 154(b) by 0 days.

(21) Appl. No.: 69/467,264

(22) Filed: Sep. 28, 1999

#### (30) Foreign Application Priority Data (51) Int. CL<sup>+</sup> ...... H01L 23/02; H01L 23/34

(S2) U.S. Cl. 257/686, 257/776, 257/780, 257/723, 257/724; 257/782; 257/783 (58) Field of Search 257/738, 780, 782, 783, 778, 777, 774

References Cited

#### U.S. PATENT DOCUMENTS

|  | 5,731,633 | ٨ | + | 3,1996  | Clayton        | 257)723 |  |

|--|-----------|---|---|---------|----------------|---------|--|

|  | 5,784,264 | Α | + | 7/1998  | Tanioka        | 361,809 |  |

|  | 5,854,507 | Α | * | 12/1996 | Mirenati et al | 257/686 |  |

|  | 5,977,640 | A | * | 11/1999 | Bertin et al.  | 251)717 |  |

| 6,025,648 | ٨   | + | 2/2000  | Takabashi et al | 257)71  |

|-----------|-----|---|---------|-----------------|---------|

| 6,040,630 | ٨   | + | 3,2000  | Panches et al   | 257578  |

| 6,051,878 | A.  | ٠ | 42000   | Aksem et al     | 25'068  |

| 6,089,793 | A   |   | 5(2000) | Marayama et al  | 301.68  |

| 6,101,100 | A   |   | 8/2000  | Lords           | 361,76  |

| 6,137,164 | A   |   | 10.2000 | Yew et al       | . 25/68 |

|           |     |   |         | Che             |         |

| 6,185,127 | ш   | + | 2/2001  | Sepho et al     | 257)68  |

| 4,990,915 | Dri |   | 6/2004  | Tiesense        | 909/99  |

\* cited by examiner

Primary Examiner-Steve Lofe

Assistant Examiner—Nitin Paolds (74) Attorney, Agent, or Firm—Merchant & Gould, P.C.

ABSTRACT

A semiconductor chip module includes a chip-mounting member having opposite first and second surfaces, a set of ciscuit traces, and a plantility of planed through holes that extend through the first and second surfaces and that are connected to the circuit traces. A dielectric tape member bonds adhesively a semiconductor chip on the chip-mounting member. A first conductor unit connects electrically centact pads on a pad mounting surface of the seni-confactor chip and the circuit traces. A plurality of solder balls are disposed on one of the first and second surfaces of the chip-mounting member, are aligned with and are con-nected to the plated through holes in the chip-mounting member, respectively.

#### 8 Claims, 9 Drawing Sheets

#### 020 United States Patent

(54) SEMICONDUCTOR DEVICE WITH A MULTI-LEVEL INTERCONNECT STRUCTURE AND METHOD FOR MAKING

(76) Inventor: Yu-Nung Shon, 4F, No. 52, Sec. 2, Chang-Shan N. Rd., Taipei City (TW)

(\*) Notice: Subject to any dischainer, the term of this putent is extended or adjusted under 35 U.S.C. 154(b) by 0 days.

(21) Appl. No.: 10/716,948

(22) Filed: Nov. 19, 2003

Prior Publication Data US 2004/0135257 A1 Jul. 15, 2004

Foreign Application Priority Data

(51) Int. Cl. H01L 23/48

(2006.01) (52) U.S. CL .... 257/758 (10) Patent No.: US 7,176,573 B2

(45) Date of Patent: Feb. 13, 2007

(58) Field of Classification Search .... 257/734-738, 700; 438/118 See application file for complete search history.

References Cited

U.S. PATENT DOCUMENTS

\* cited by examiner

Primary Econoce-Nation W. Ha

ABSTRACT

A semiconductor device includes a semiconductor die ond a multi-level interconnect structure that has a first insulating layer formed on the die, conductive horizontal bodies, each toyer formed on the day, conductive honology and of the die of which is connected to a respective bonding pad of the die and has an extension formed on the first insulating layer, a second insulating layer formed on the first insulating layer, as and conductive vertical bodies, each of which is connected to the extension of a respective conductive horizontal body and extends through the second insulating layer.

#### 20 Claims, 4 Drawing Sheets

020 United States Patent

Shen

(54) METHOD FOR MAKING A CIRCUIT PLATE (76) Inventor: Yu-Nung Shen, 4F, No. 52, Sec. 2, Chung-Shan N. Rd., Taipei City (TW)

(\*) Notice: Subject to any disclaimer, the term of this patent is extended or adjusted under 35 U.S.C. 154(b) by 312 days.

(21) Appl. No.: 11/166,058

(22) Filed: Jun. 24, 2005

Prior Publication Data US 2006/0000635 Al Jun. 5, 2006

(200)Foreign Application Priority Data

(51) Int. CL HOSK 3/02

(2006.01) (2006.01)

29/852; 29/835; 29/846; 29/847; 29/848

See application file for complete search history.

(45) Date of Patent:

References Cited U.S. PATENT DOCUMENTS

(10) Patent No.: US 7,383,630 B2

Jun. 10, 2008

4 cited by examiner

Primary Examiner—C. J Arbes (74) Attorney, Agent, or Firm—Ladas and Pony 1LP

ABSTRACT

A method for making a circuit plate includes: forming first holes in an insulating layer, forming a conductive layer on the insulating layer such that a portion of the conductive layer fills the first holes; grinding the conductive layer such that the pertion of the conductive layer remains in the first holes to form a pattern of conductive traces; forming a dielectric protective layer that covers the insulating layer and the conductive traces, forming a pattern of second holes in the protective layer such that a portion of each of the conductive traces is accessible through a respective one of the second holes; and forming conductive bumps that are respectively connected to the conductive traces.

#### 14 Claims, 5 Deaving Sheets

#### (12) United States Patent Shen

#### (54) METHOD FOR MAKING A CIRCUIT PLATE

- (76) Inventor: Yu-Nung Shen, 4F, No. 52, Sec. 2, Chung-Shan N. Rd., Toipei City (TW)

- (\*) Notice: Subject to any disclaimer, the term of this patent is extended or adjusted under 35 U.S.C. 154(b) by 312 days.

- (21) Appl. No.: 11/166,058

- (22) Filed: Jun. 24, 2005

- (65) Prior Publication Data

- US 2006/0000635 A1 3as. 5, 2006

- (51) Int. Cl. 1001K 379

- H01K 3/18 (2006.01) H05K 3/02 (2006.01)

- (S2) U.S. Cl. 29/882, 29/835, 29/846, 29/847, 23/948 (S8) Field of Classification Search 29/846, 847, 848, 852

- 29/846, 847, 848, 8 See application file for complete search history.

#### (10) Patent No.: US 7,383,630 B2 (45) Date of Patent: Jun. 10, 2008

#### (56) References Cited

#### U.S. PATENT DOCUMENTS

| 6,676,952    | B2 * | 1/2004 | Janil         |

|--------------|------|--------|---------------|

|              |      |        | Hsu et al     |

| 2901/0040290 | AL*  | H:2000 | Sakusai et al |

\* cited by examiner

Primary Enminer—C. J Arbes (74) Attorney, Agent, or Firm—Ladas and Porty LLP

#### 7) ABSTRACT

A method for making a circuit plate includes: forming first holes in an insulating layer, forming a conductive layer on the insulating layer such that a portion of the conductive layer fills the first holes; grinding the conductive layer such that the portion of the conductive layer remains in the first holes to form a purtous of conductive traces; forming a dielectric partective layer that covers the insulating layer and the conductive layer such that a portion of each of the conductive traces is accessible through a respective one of the second holes; and forming conductive bumps that are respectively connected to the conductive traces.

#### 14 Claims, 5 Dearring Sheets

#### (12) United States Patent Chen

(10) Patent No.: US 6,437,448 B1 (45) Dute of Putent: Aug. 20, 2002

#### (54) SEMICONDUCTOR DEVICE ADAPTED FOR MOUNTING ON A SUBSTRATE

- (76) Inventor: I-Ming Chen, No. 60, Lanc 328, Li-Shan St., Nei-Hu Dist., Taipei City

- (\*) Notice: Subject to any disclaimer, the term of this patent is extended or adjusted under 35 U.S.C. 154(b) by 0 days.

- (21) Appl. No.: 09/765,793

- (22) Filed: Jun. 18, 2001

#### Related U.S. Application Data

- (63) Centinuation in part of application No. 49/725,431, filed on Nov. 29, 2000.

- (30) Foreign Application Priority Data

| Oct  | . 21, 2000 (TW)                                                         |

|------|-------------------------------------------------------------------------|

| (51) | Int. Cl.7                                                               |

| (52) | U.S. Cl257/777; 257/737                                                 |

| (58) | Field of Search 257/737, 736,<br>257/777, 778, 779, 780, 781, 782, 784, |

#### (5t) References Cited

#### U.S. PATENT DOCUMENTS

| 5,222,014 A * 6 | 1993 Lin | 381/414 |

|-----------------|----------|---------|

|-----------------|----------|---------|

| 5,990,546 | Α | * | 11/1999 | Igasashi et al | 25'07'00 |

|-----------|---|---|---------|----------------|----------|

|           |   |   |         | Moriyama       |          |

|           |   |   |         | Hobo et al     |          |

|           |   |   |         | Chen           |          |

<sup>\*</sup> cited by exerciser

Primary Examiner—Vict Q. Ngayen Assistant Examiner—Osvid Neu CAD Attorney, Agent, or Firm—Christianus O'Conney,

#### (57) ABSTRACT

Johnson Kindness PLLC

A method for manufacturing a semiconductor device includes the steps of providing a sunticonductor chip baving a pad-mounting surface with a bonding pad, forming a library on the bonding pad, forming a photoresist layer on the pad-mounting surface, forming a second bump which protrudes from the first bump through an upper surface of the photoresist layer, and forming a conductive body on the second bump. The conductive body has an anchor portion connecting electrically with and encapsulating an apper portion of the second bump, and a contact portion offset from the anchor portion and adapted to be connected to a substrate.

#### 11. Claims, 4 Drawing Sheets

## 全球半导体和内存市场

内存占全球半导体四分之一的产量

## 数据存取需求爆炸性的成长

1 ZB = 10<sup>21</sup> bytes = 1000,000,000,000 GB

大数据显示"移动/计算应用中的广泛部署而正在创建。数据是未来十年的新"石油"。

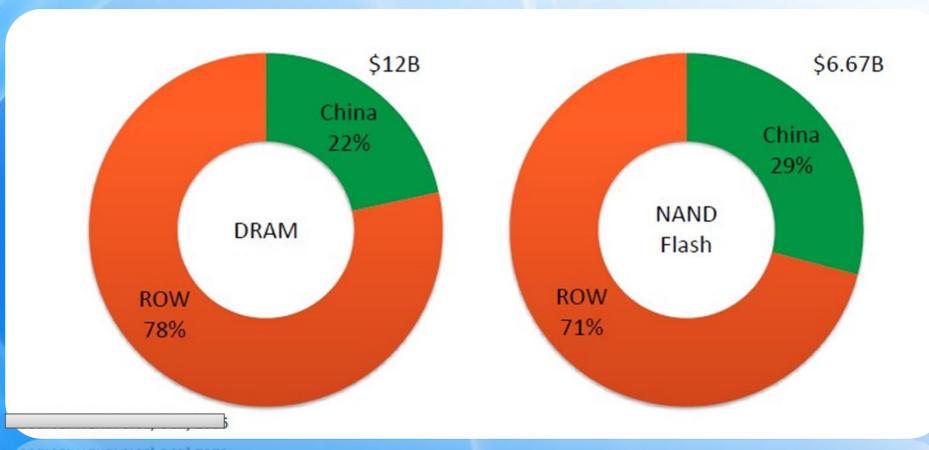

## 中国的内存需求

Source: TrendForce, Oct., 2015

隨著PC智能手機的興起,中國國內DRAM和NAND閃存消費量急劇增加。中國占世界記憶產量的30%左右,其中大部分都是由國外進口製造。

## NAND Flash需求

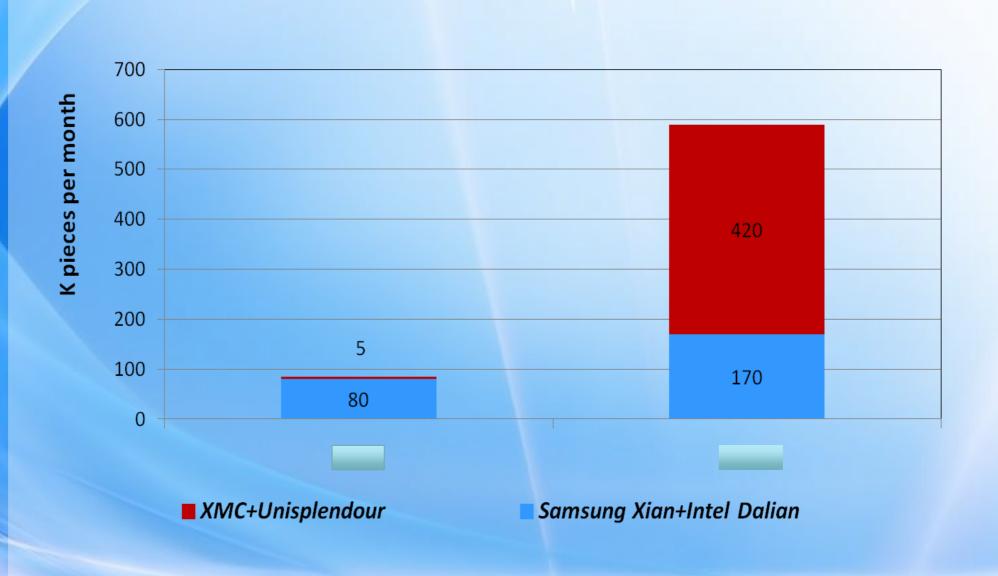

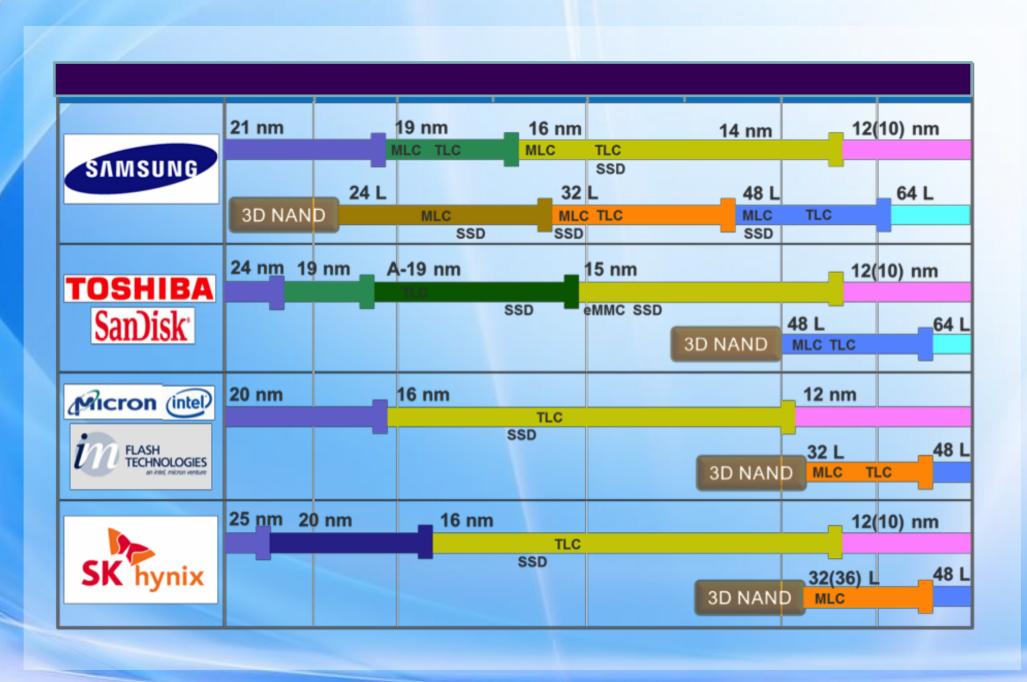

## 各厂3D封装技术进程

## 全球半导体中心的战略图

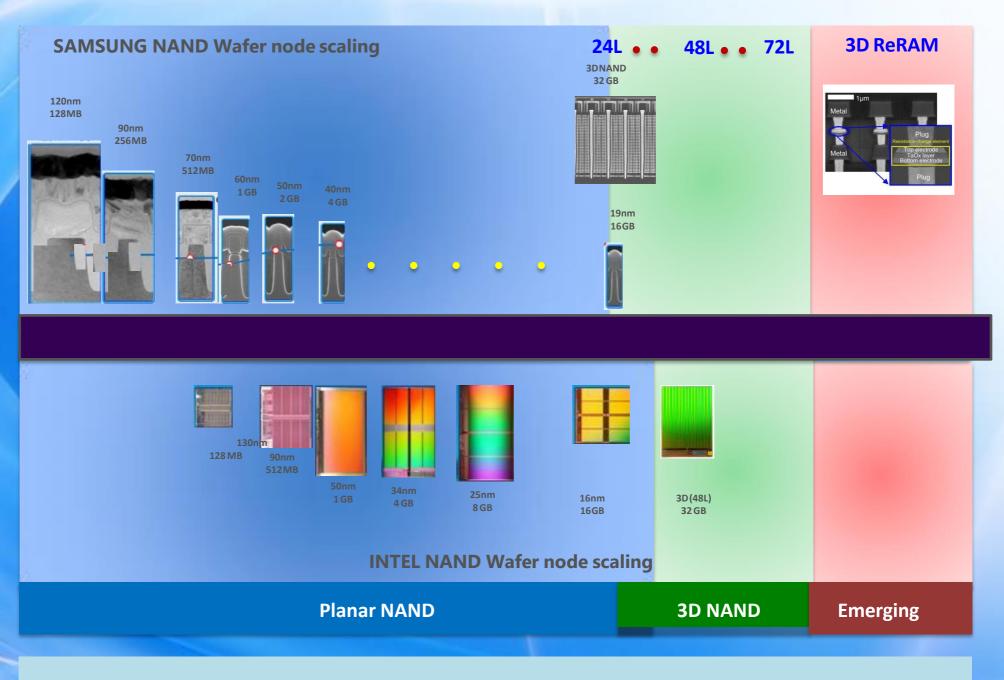

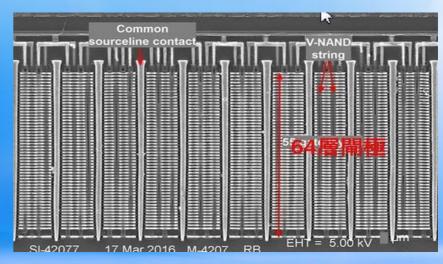

## 3D NAND发展进程

3D NAND技术提供的扩展经济效益显著降低了

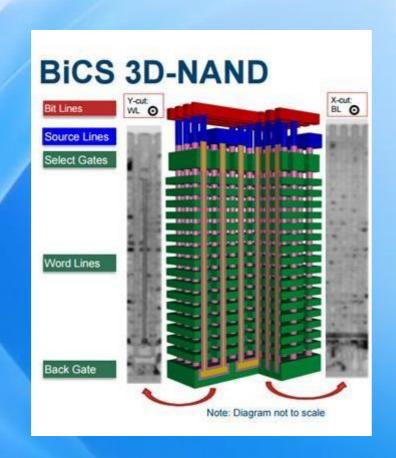

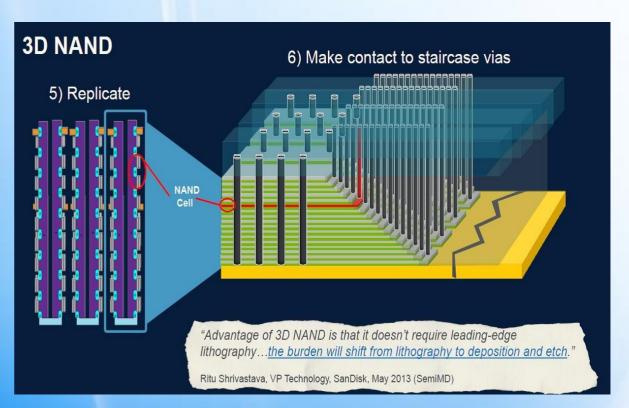

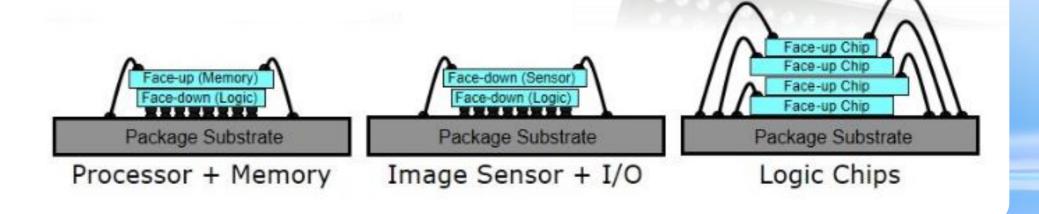

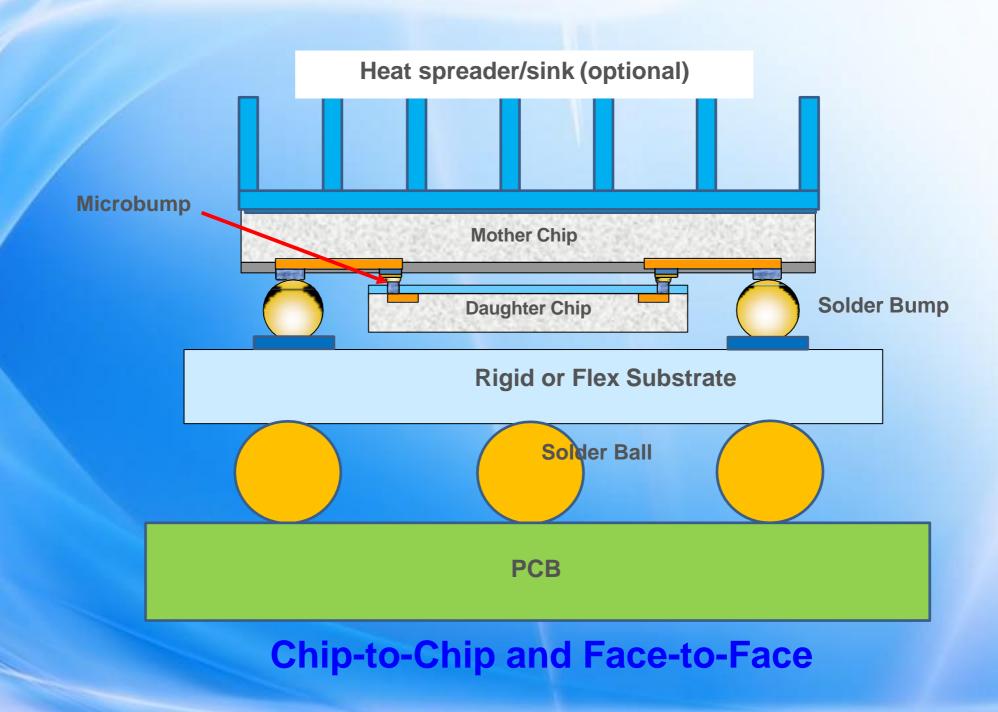

## 3D封装技术概念图

## 3D封装技术应用范围

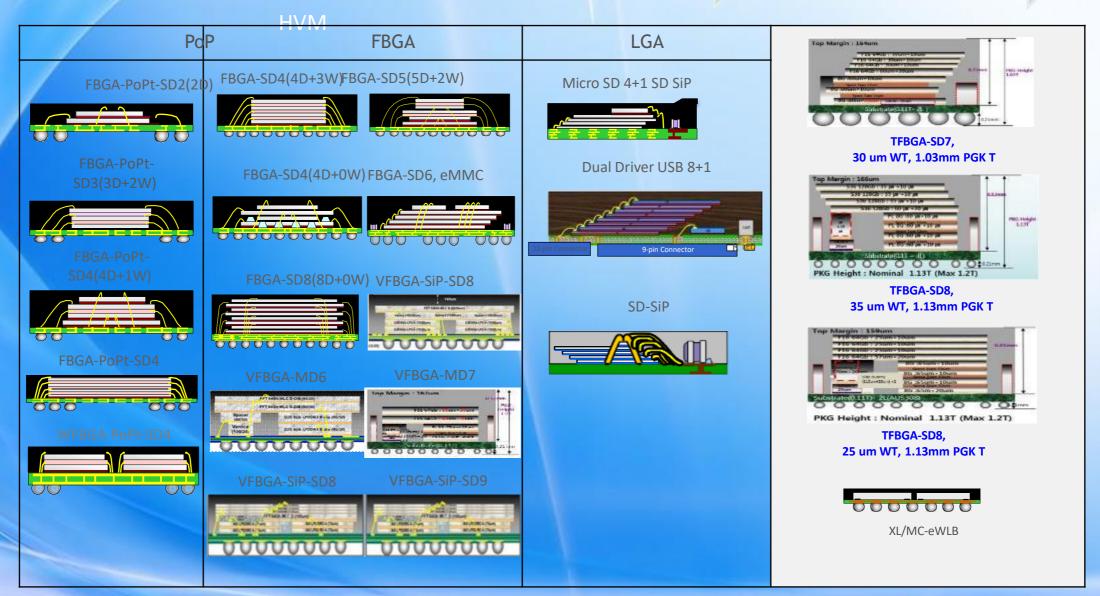

## 各种堆栈方式应用范围

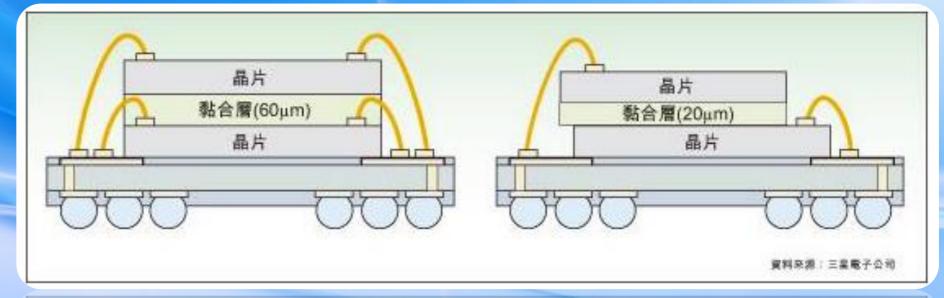

## 记忆替封装趋势

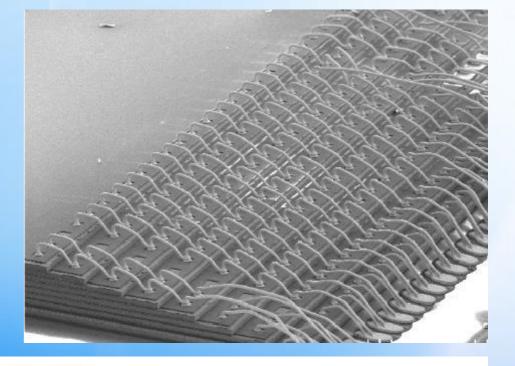

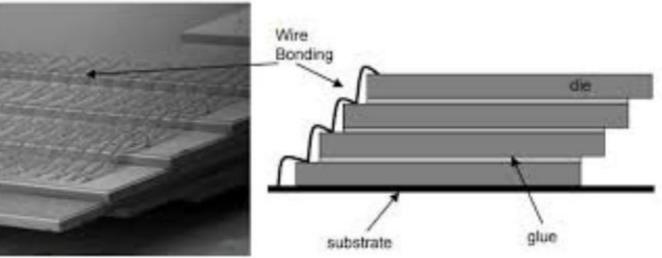

## 目前技术

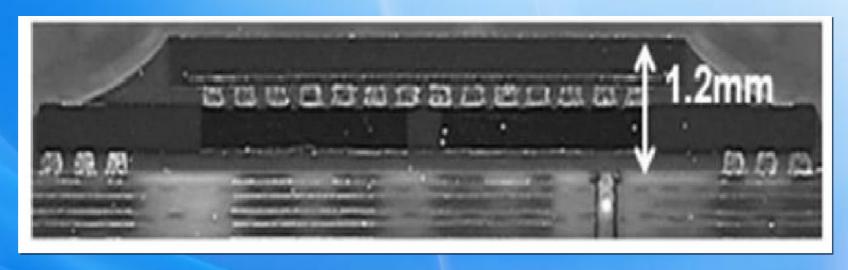

### 趋势

L=1.4mm, T=1.2mm, V=1.0mm, W=0.8mm, U=0.65mm, X=0.50mm

## LFBGA-SD8 (NAND)

### **Package Features**

LFBGA 14x18mm 152LD

• NAND Die Size: 9.7x17.1mm

Device: 20nm Non-LowK NAND

Wafer thickness: 60um

Mold cap: 0.84mm

2-lyr / 0.13mmT laminate substrate

### **Key Technologies**

- 20nm NAND die

- 0.5mm overhang W/B with 60um die thickness

- 2-passes DA for the 8 dies stack

#### **Current Status**

HVM since 2024

### 内存堆栈芯片封装- MIXED (FBGA-SD6) NAND + DDR + CONTROLLER

### **Package Features**

- VFBGA-SD6 11.5x13mm 153LD

- Nand flash Die Size: 10.33x8.12mm

- DDR Die Size: 6.32x2.69mm

- Controller Die Size: 6.79X1.82mm

- 0.13mm, 3-lyr coreless substrate

### **Key Technologies**

- 0.13T odd layer substrate handing

- SSB loop for die to die and die to substrate

- Warpage control w/ 3L substrate

### **Current Status**

HVM since 2024

## FLGA-SD9 (USB)

### **Package Features**

- FLGA 11.1x16mm

- Memory Die Size : 8.2x11.1mm

- Controller Die Size: 2.9x2.4mm

- Device: 19nm Non-LowK + 65nm Lowk

Controller

- Wafer thickness: 68um x 8 dies + 150um

Controller

- 2-lyr / 0.21mmT laminate substrate

### **Key Technologies**

- 19nm NAND die

- 8-Die Stack with Die-to-die bonding

- One-pass for the 8 NAND dies stack

#### **Current Status**

HVM

## **Memory Stacked-Die**

### **Package Features**

- FBGA 11.5x13mm 221LD e-MCP

- 4.115x1.385(Controller): 60um

- 9.647x8.070(DRAM): 75um

- 1.208x7.171(Nand): 60um

- 9.00x8.00 (Film spacer) : 53um

- 2-lyr / 0.41mmT laminate substrate

### **Key Technologies**

- 60um NAND flash die

- Film spacer application

- **Dolmen and NAND cascade structure**

#### **Current Status**

HVM from '2024

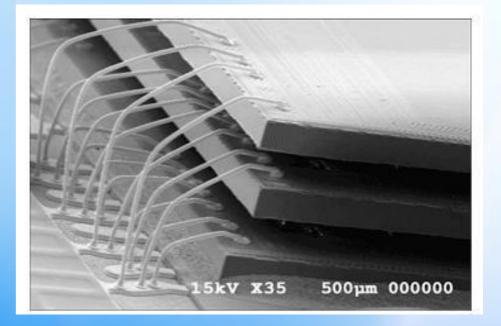

## 堆栈硅模块连接在基板上

## 半导体3D堆栈方式

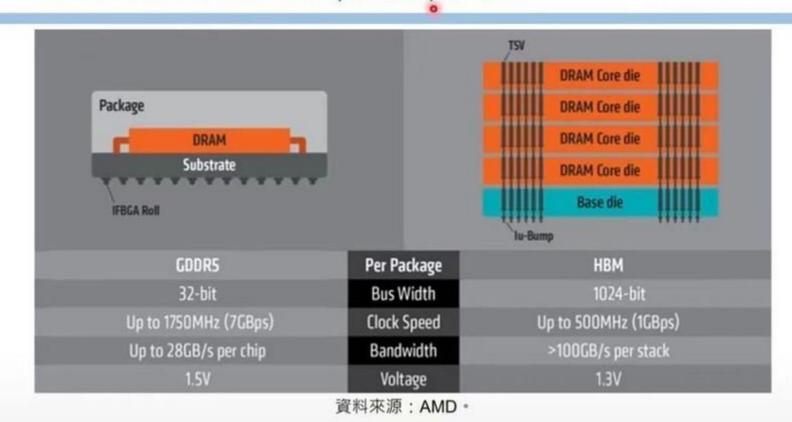

### □ 高頻寬記憶體(HBM)相關供應鏈

### □ 動能隨機存取記憶體(DRAM)的差異

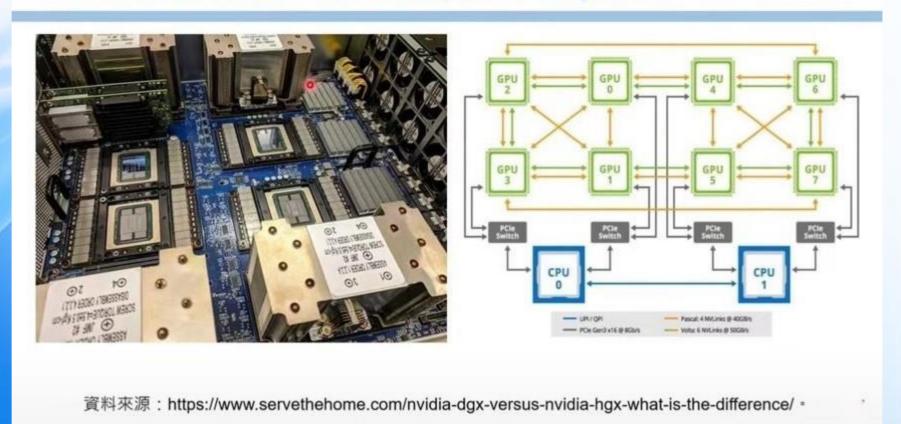

### ■ NVIDIA Tesla P100 8x SXM2 GPU system

### □ 圖形處理器(GPU)與高頻寬記憶體(HBM)